# 应用手册

晶体振荡电路设计注意事项

#### 适用范围:

● SYM32 全系列芯片

## 1 文档说明

本应用手册将详细介绍 SYM32 系列微控制器的外部晶体电路设计及 Layout 的注意事项。

## 2 晶体振荡器及振荡器电路

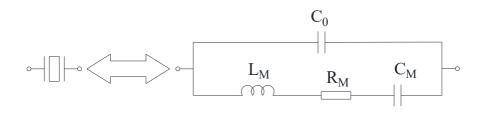

石英晶体振荡器是一种将电能转换为机械能的压电器件。该变换发生在共振频率。如图 2-1 中显示描述石英晶体的等效电路。

图 2-1 石英晶体的等效电路

#### 3 振荡电路参数计算

振荡裕量,是负阻与谐振器等效串联电阻的比值。一般来说,振荡裕量大于或等于5倍。

激励功率,是指振荡电路工作时谐振器的功耗,激励功率大于晶体谐振器的功率可能给晶体谐振器带来损坏,一般要把激励功率控制在规格要求的范围内。

振荡裕量和激励功率的计算请询问晶体供应商,对设计可靠的振荡电路很有必要。

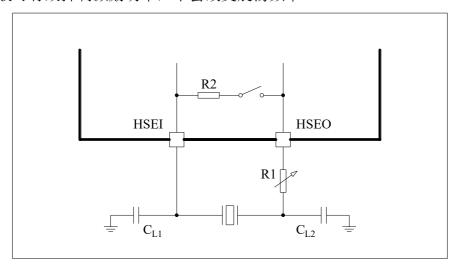

阻尼电阻,一般可有效抑制激励功率,不会改变震荡频率。

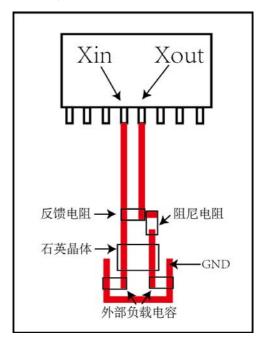

图 3-1 晶体振荡器电路

#### 负载电容的计算

无源晶体信号质量较差,通常需要精确匹配外围电路(用于信号匹配的电容、电阻等),更换不同频率的晶体时周边配置电路也需要做相应的调整。

匹配电容  $C_{L1}$ 、 $C_{L2}$  的容值必须根据所选谐振器的参数及 PCB 布局进行调整, 计算方法为:

$$C_L = \frac{C_{L1} \times C_{L2}}{C_{L1} + C_{L2}} + C_0$$

其中,

CL为谐振器标称负载电容值;

$C_0$ 为 PCB 走线分布电容值,一般可取值 4pF~6pF;

$C_{L1}$  和  $C_{L2}$  为外接的 2 个匹配电容,通常  $C_{L1}$  和  $C_{L2}$  相同。

若采用标称 CL为 15pF 的谐振器,则匹配电容常见取值为 20pF。

若芯片输出的激励功率超过谐振器的标称值,可通过增加 R1 电阻的阻值以解决。

注意:由于晶体特性及 PCB 走线千差万别,当采用经验公式计算出的匹配电容不能让 HSE 振荡器输出理想时钟信号时,建议联系晶体厂家对 R1、 $C_{L1}$ 、 $C_{L2}$ 进行调整以达到最佳匹配。

### 4 Layout 注意事项

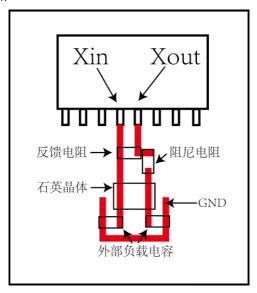

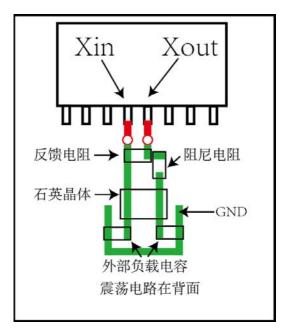

MCU 外接晶体谐振器一般有反馈电阻、阻尼电阻、石英晶体、外部负载电容等组成,如图 4-1 所示,布局时要注意以下几点。

图 4-1 MCU 与外部晶体谐振器的布局

- 晶体内部是石英晶体,如果不慎掉落或受不明撞击,石英晶体易断裂破损,所以晶体的放置 远离板边,靠近 MCU 的位置布局。

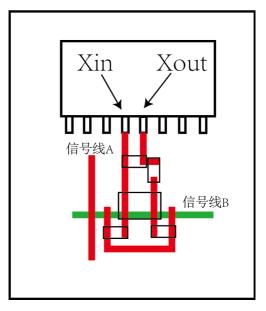

- 避免将任何其他信号路由到晶体区域。图 4-2 所示信号线走线离晶体太近,容易互相干扰,

- 为了最大限度地降低寄生天线和寄生耦合现象引起的噪声敏感度,晶振,电容(需要时)和 MCU 振荡器引脚之间的距离应尽可能短。图 4-3 所示晶体与 MCU 距离太远,走线过长

- 尽可能的保证晶体周围不要摆放其他元器件,以免器件之间互相影响,晶体周围尽量不要有其他过孔走线,晶体下方不打过孔。图 4-4 所示晶体和 MCU 不在同一面,且有过孔。

- 所有连接晶体输入/输出端的导线尽量短,以减少噪声干扰及分布电容对晶体的影响。

- 使晶体、外部电容器(如果有)与 IC 之间的信号线尽可能保持最短。当非常低的电流通过 IC 晶体振荡器时,如果线路太长,会使它对 EMC、ESD 与串扰产生非常敏感的影响。而且长 线路还会给振荡器增加寄生电容。

图 4-2 信号线太靠近晶体谐振器

图 4-3 振荡电路和 MCU 之间距离太远走线过长

图 4-4 振荡电路与 MCU 不在同一面且有过孔

# 5 版本记录

| 版本     | 修订日期       | 修订说明 |

|--------|------------|------|

| Rev1.0 | 2022-07-11 | 初始版本 |